# **Solid State Devices**

# **4B6**

Lecture 4 – MOSFET (i)

Daping Chu

Lent 2016

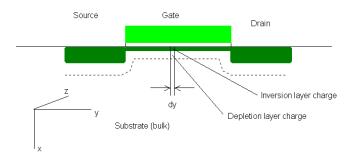

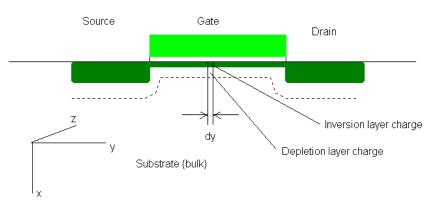

#### **MOSFET** simple analysis

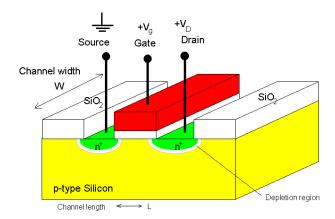

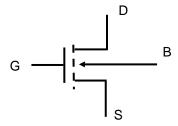

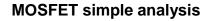

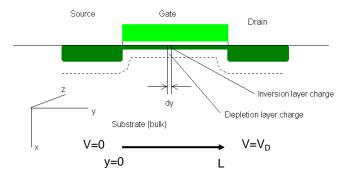

We consider a simplified MOSFET structure with the source grounded and the bulk floating.

The voltages applied to the gate and the drain determine the carrier density and the level of conduction in the channel (ideal MOS capacitor).

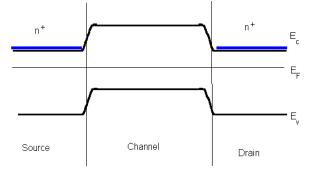

### Band structure in silicon adjacent to oxide layer

Simple behaviour may be understood by considering the band structure in the silicon where the channel is formed.

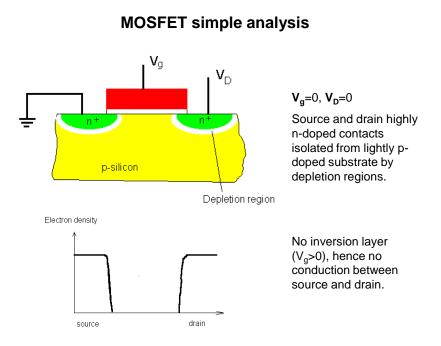

$V_q=0$ , (flat band)  $V_D=0$ , equilibrium ie  $I_D=0$ .

$E_F$  close to conduction band edge in contacts.

$E_F$  energy closer to valence band edge in channel.

No free electrons in channel.

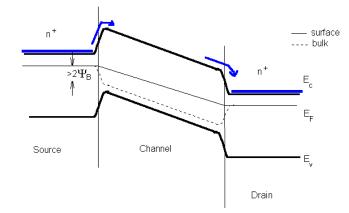

### Band structure in silicon adjacent to oxide layer

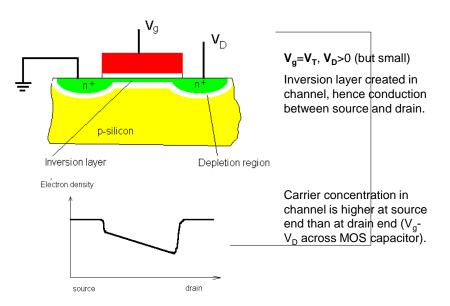

$V_{q}>0$ ,  $V_{p}>0$  (but small), leading to resistive drop in channel.

$E_F$  closer to conduction band edge in channel near to surface.

E<sub>F</sub> energy closer to valence band edge lower down.

Some electrons overcome barrier and transfer to drain.

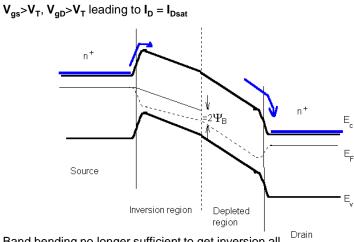

### Band structure in silicon adjacent to oxide layer

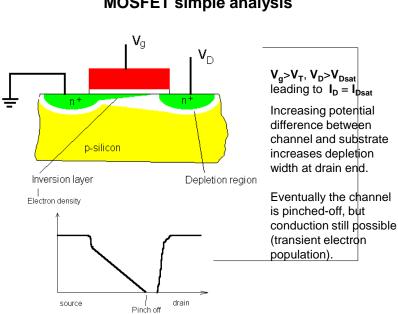

Band bending no longer sufficient to get inversion all <sup>Drain</sup> along channel near to surface.

Electron population stable only up to edge (but can't get back) so carry on to drain.

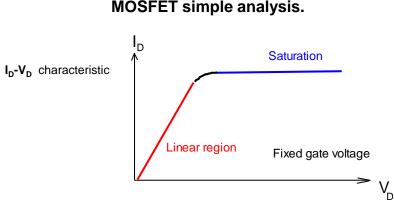

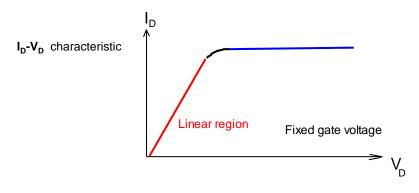

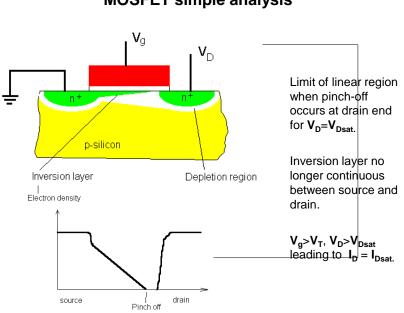

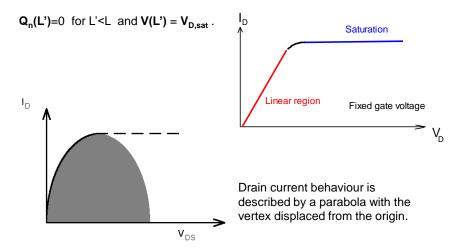

Linear region occurs at low drain voltages where the channel is continuous between the source and the drain.

At larger drain voltages the channel is no longer inverted at the drain end so that the current no longer increases in response to a larger drain voltage.

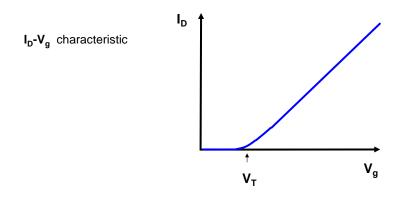

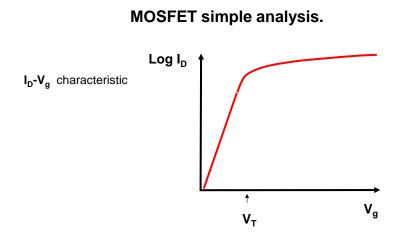

#### **MOSFET** simple analysis.

On a linear scale  $I_D$  simply increases with increasing  $V_g$  above  $V_{\ensuremath{\mathcal{T}}\xspace},$  as expected from the previous analysis.

Below  $V_{T}$ , the current is expected to be zero.

On a log scale  $I_D$  is seen to deviate from this behaviour at low gate voltages, particularly below  $V_7$ , where simple analysis predicts  $I_D$ =zero.

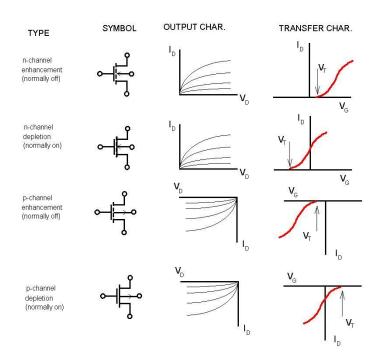

### **Types of MOSFET**

Simple description for n-channel MOSFET with no channel present at zero gate voltage

Four possible choices depending on channel type (n-channel or p -channel) and threshold voltage with respect to drain voltage range (enhancement or depletion).

This wide range of choice give circuit designers great flexibility.

Conventional symbols.....

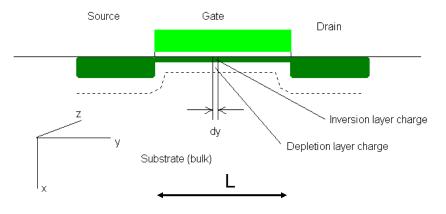

### Simple analysis

Inversion layer continuous from source to drain.  $\mathbf{I}_{\mathrm{D}}$  depends on:

Qnareal charge density in inversion layer.μcarrier mobility in inversion layer.dV/dypotential gradient along channel.

Assumptions:

- (1) Ideal MOS capacitor.

- (2) Constant carrier mobility in inversion layer.

- (3) Uniform doping in substrate.

- (4) No reverse leakage current (to undepleted substrate).

- (5) Drift current only.

- (6) Axial electric field >> longitudinal electric field.

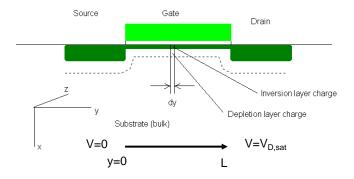

Inversion layer charge  $Q_n$ . Depletion layer charge  $Q_B$ . Channel length L. Channel width z.

Surface charge density at y:

$$Q_s(y) = C_{ox}V_{ox}(y) = [\psi_s(y) - V_G]C_{ox}$$

where  $\bm{C}_{ox}$  is the oxide cap. and  $\bm{V}_{ox}$  is the voltage across the oxide.

### **Gradual channel approximation**

Inversion layer charge:

$$Q_n(y) = Q_s(y) - Q_B(y) = -[V_G - \psi_s(y)]C_{ox} - Q_B(y)$$

where  $\mathbf{Q}_{\mathbf{B}}(\mathbf{y})$  is the bulk charge (ionised acceptors) in the depletion layer.

At inversion,

$$\psi_s(y) \approx 2\psi_B + V(y)$$

From the MOS capacitor, the depletion width  ${f w}$  is given by

$$w = \sqrt{\frac{2\varepsilon_s \psi(inv)}{eN_A}}$$

So we get

$$Q_B(y) = -eN_A w = -\sqrt{2e\varepsilon_s N_A [2\psi_B + V(y)]}$$

### **Gradual channel approximation**

Therefore the inversion layer charge is

$$Q_n(y) = -[V_G - V(y) - 2\psi_B]C_{ox} + \sqrt{2e\varepsilon_s N_A [2\psi_B + V(y)]}$$

This inversion layer charge gives rise to a current given by:

mobility X charge per unit area X electric field X channel width

$$I = \mu_n |Q_n| \frac{dV}{dy} z$$

Current flow is continuous from source to drain but voltage drop depends on surface potential.

Need to integrate separate contributions to get total voltage drop for given current.

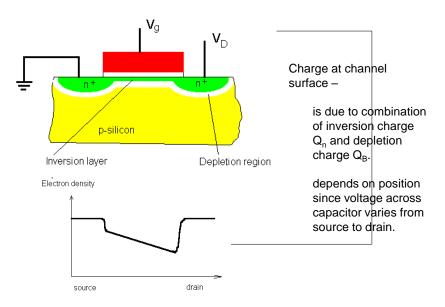

## Gradual channel approximation

$$I = \mu_n |Q_n| rac{dV}{dy} z$$

but dV=I.dR

So that the resistance **dR** of a slice **dy** is  $dR = \frac{dy}{z\mu_n|Q_n|}$

So that

$$Idy = z\mu_n |Q_n(y)| dV$$

Substituting

$$Idy = z\mu_n \left\{ \left[ V_G - V(y) - 2\psi_B \right] C_{ox} - \sqrt{2 \, e\varepsilon_s N_A \left[ 2\psi_B + V(y) \right]} \right\} dV$$

Integrating y from 0 to L ie. V(y) from 0 to  $V_D$  gives

$$I_{D} = \frac{z}{L} \mu_{n} C_{ox} \left\{ \left[ V_{G} - 2\psi_{B} - \frac{V_{D}}{2} \right] V_{D} - \frac{2}{3} \sqrt{\frac{2e\varepsilon_{s} N_{A}}{C_{ox}} (V_{D} + 2\psi_{B})^{\frac{3}{2}} - (2\psi_{B})^{\frac{3}{2}}} \right\}$$

### **Gradual channel approximation**

Integrating y from 0 to L ie. V(y) from 0 to  $V_D$  gives

$$I_{D} = \frac{z}{L} \mu_{n} C_{ox} \left\{ \left[ V_{G} - 2\psi_{B} - \frac{V_{D}}{2} \right] V_{D} - \frac{2}{3} \sqrt{\frac{2e\varepsilon_{s} N_{A}}{C_{ox}} (V_{D} + 2\psi_{B})^{\frac{3}{2}} - (2\psi_{B})^{\frac{3}{2}}} \right\}$$

Expanding the final term as a series, for small  $V_D,\,V_D{}^3$  and higher powers can be neglected:

$$I_D \approx \frac{z}{L} \mu_n C_{ox} \left\{ \left[ V_G - V_T \right] V_D - \left( \frac{1}{2} + \frac{\sqrt{e\varepsilon_s N_A / \psi_B}}{4C_{ox}} \right) V_D^2 \right\}$$

# Gradual channel approximation – linear region

$V_D << V_G - V_T$ :

$$I_D \approx \frac{z}{L} \mu_n C_{ox} [V_G - V_T] V_D$$

Channel conductance:

$$g_D = \frac{\delta I_D}{\delta V_D} = \frac{z}{L} \mu_n C_{ox} [V_G - V_T]$$

Transconductance:

$$g_m = \frac{\delta I_D}{\delta V_G} = \frac{z}{L} \mu_n C_{ox} V_D$$

Slope of linear region depends on excess gate drive

$$g_D = \frac{\delta I_D}{\delta V_D} = \frac{z}{L} \mu_n C_{ox} [V_G - V_T]$$

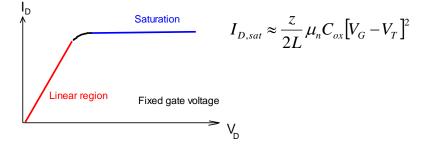

### Gradual channel approximation – saturation region

At the onset of saturation,  $\mathbf{Q}_{n}(\mathbf{L})=0$ .

$$Q_n(L) = -\left[V_G - V_{D,sat} - 2\psi_B\right]C_{ox} + \sqrt{2e\varepsilon_s N_A \left[2\psi_B + V_{D,sat}\right]} = 0$$

#### Gradual channel approximation - saturation region

So that

$$\left[V_{G} - V_{D,sat} - 2\psi_{B}\right]C_{ox} = \sqrt{2e\varepsilon_{s}N_{A}\left[2\psi_{B} + V_{D,sat}\right]}$$

which can be solved as a quadratic in  $V_{D,sat}$ :

$$V_{D,sat} = V_G - 2\psi_B + \left(\frac{e\varepsilon_s N_A}{C_{ox}^2}\right) \left(1 - \sqrt{1 + \frac{2V_G C_{ox}^2}{e\varepsilon_s N_A}}\right)$$

### Gradual channel approximation - saturation region

Substituting into the equation for  $\mathbf{I}_{\mathbf{D}}$  and simplifying

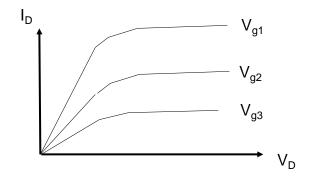

No dependence on  $V_{\rm D}$  so no conductance (current is fixed) but still a transconductance

$$g_{m,sat} = \frac{\delta I_{D,sat}}{\delta V_G} = \frac{z}{L} \mu_n C_{ox} [V_G - V_T]$$

### Gradual channel approximation - saturation region

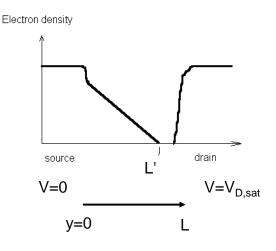

When  $V_{D}\!\!>\!\!V_{D,sat}$  the end of the inversion point (L') moves closer to the source.

### Gradual channel approximation – saturation region

Resistance of inversion layer reduces only slightly, so that  $dl_D/dV_D=1/r_d$  is non-zero (increase slope of dashed line).

Current essentially independent of  $V_{\text{D}}$  in saturation but still depends on gate voltage.

Most important operating region of transistor:  $V_g > V_T$

#### Worked example

Find the drain current for an n-channel silicon MOSFET, with z/L ratio of  $100\mu m/1\mu m$ , operating with drain, gate, source and substrate voltages of 5, 3, 0 and 0V respectively. The gate oxide thickness is  $0.1\mu m$ , the substrate doping density is  $1\times10^{15} \text{cm}^{-3}$ , the channel mobility 500 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> and the threshold voltage is 1V.

To find the drain current we first need to decide whether the transistor is operating in the linear or the saturated regime. The saturated drain voltage is given by

$$V_{D,sat} = V_G - 2\psi_B + \left(\frac{e\varepsilon_s N_A}{C_{ox}^2}\right) \left(1 - \sqrt{1 + \frac{2V_G C_{ox}^2}{e\varepsilon_s N_A}}\right)$$

The substrate voltage is

$$\Psi_{B} = \left(\frac{kT}{e}\right) \ln\left(\frac{N_{a}}{n_{i}}\right) = 0.3 V$$

## Worked example

and the oxide capacitance is

$$C_{ox} = \frac{\varepsilon_o \varepsilon_{ox}}{t_{ox}} = \frac{8.8 \times 10^{-12} \times 3.9}{10^{-7}} = 3.43 \times 10^{-4} \ Fm^{-2}$$

So that the saturated drain voltage is

$$V_{D,sat} = 3 - 2 \times 0.3 + 0.14 \times (-5.6) \sim 1.6 V$$

With a drain voltage of 5V the drain current is saturated and so is given by

$$I_{D,sat} \approx \frac{z}{2L} \mu_n C_{ox} [V_G - V_T]^2 = 3.43 \, mA$$